Common-Source(CS) Stage : Load resistor

앞 장에서 Common-Source Amplifier의 Large/small signal 분석을 진행했다. 그 결과 Input Voltage와 Output Voltage의 Voltage gain을 구했다.

위 회로의 Gain은 다음과 같은 식으로 표현할 수 있었다.

Common-Source Stage의 Voltage gain을 키워보자.

위의 식을 사용해 Gain을 키우려면 우리는 gm을 키우거나 RD를 키워야 한다.

먼저 gm을 키우기 위해 gm에 대한 식을 살펴보자.

위의 식을 사용해 gm을 키우려면 ID는 고정인 상태에서 VGS-VTH의 값을 줄여야 한다. ID는 고정인 상태에서 VGS-VTH의 값을 줄이려면 W/L값을 키워야 한다. 즉, MOSFET의 aspect ratio를 키우면 gm을 키울 수 있어 Voltage gain이 커지게 된다. MOSFET의 Size가 커지게 되면 그로 인한 단점이 생기게 된다. MOFSET의 Input Cap인 CGS가 커지게 된다. 이로 인해 Input bandwidth가 줄어들게 된다. 따라서 Size를 원하는 대로 키울 수 없게 된다.

Voltage Gain을 키우기 위한 두 번째 방법은 RD를 키우는 것이다. ID가 변하지 않을 때 RD를 키우게 되면 ID·RD의 값이 커지게 된다. ID·RD의 값이 커지면 Vout의 DC level이 낮아진다. Vout의 DC level이 낮아지면 M1 MOSFET의 Drain 전압이 낮아지는 것이므로 VDS의 값이 줄어들게 된다. VDS의 값이 줄어들면 M1 MOSFET은 saturation 영역에서 triode 영역으로 동작 영역이 바뀔 수 있다.

위의 결과들을 확인했을 때 resistor load를 사용하는 CS amp는 gain을 키우기 어렵다는 것을 알 수 있다. Gain을 키우기 위해 다른 방식을 사용해보자.

Common-Source(CS) Stage : Diode-Connected Device

위에서 Resistor Load가 있는 Common-Source Amplifier의 분석을 진행했다. 그 결과 Resistor Load가 있는 CS amp는 gain을 키우기 어렵다는 것을 알아내었다. 이번엔 저항이 아닌 다른 소자를 연결하여 CS amp의 Voltage gain을 키워보려고 한다. 이를 활용하기 위해 우리는 MOSFET으로 구성된 Diode-Connected MOFSET을 사용하고자 한다.

위의 연결을 어떻게 분석할 수 있는지 살펴보자.

Gate와 Drain이 연결되어 있어 VG=VD가 된다.

MOSFET이 saturation영역일 때 만족하는 VDS > VGS-VTH도 만족하게 된다. 따라서 이 소자는 켜져 있다면 항상 saturation 영역에서 동작하는 MOSFET임을 알 수 있다.

이번에는 Diode-Connected MOSFET의 impedance를 알아보기 위해 Thevenin 등가 회로를 그려보면 다음과 같다.

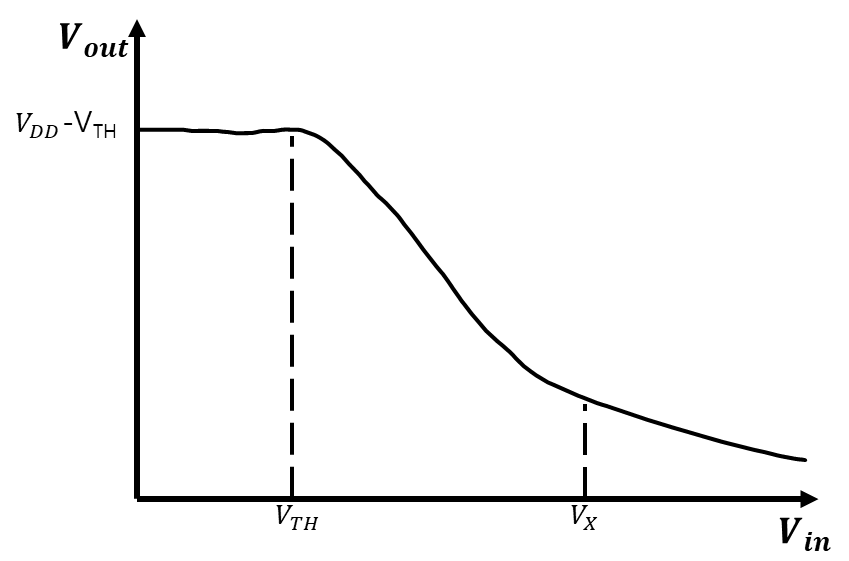

Small-Signal Model에서 Source지점을 기준으로 KCL을 적용하면 다음과 같이 표현할 수 있다.

Common-Source(CS) Stage : Diode-Connected Load Large-Signal

이제는 위에서 분석한 Diode-Connected MOSFET를 사용해 구성된 Common-Source amplifier의 대신호 분석을 해보자.

Diode-Connected MOSFET이 연결된 Common-Source amplifier는 다음과 같이 구성된다.

M2는 Diode-Connected Device이므로 켜져 있다면 saturation에서 동작할 것이다. 따라서 우리는 이번 대신호 분석에서 M1의 영역을 확인하면 된다.

먼저 Vin의 전압이 VTH보다 낮아 M1이 Off 된 상황을 살펴보자. 이 경우 M1의 Drain Current가 0이 되고 M2의 Drain Current도 0이 된다. M2의 Drain Current가 0이 되려면 VGS2-VTH=0이 되어야 한다. 따라서 VGS2=VTH가 되며 이때 Vout=VDD-VTH의 값을 가진다.

다음은 Vin의 전압이 VTH보다는 큰 경우이다. Vin의 전압이 VTH를 넘기게 되면 M1이 saturation에서 동작한다. Vin의 전압이 점점 커질수록 Vout의 값이 줄어들며 M1의 VDS의 값이 줄어들게 된다. 이로 인해 M1은 triode 영역에서 동작하게 된다. 이 부분은 앞에서 다뤘던 resistor load가 있는 CS amp에서 다뤘으므로 간략하게 정리하고 넘어간다.

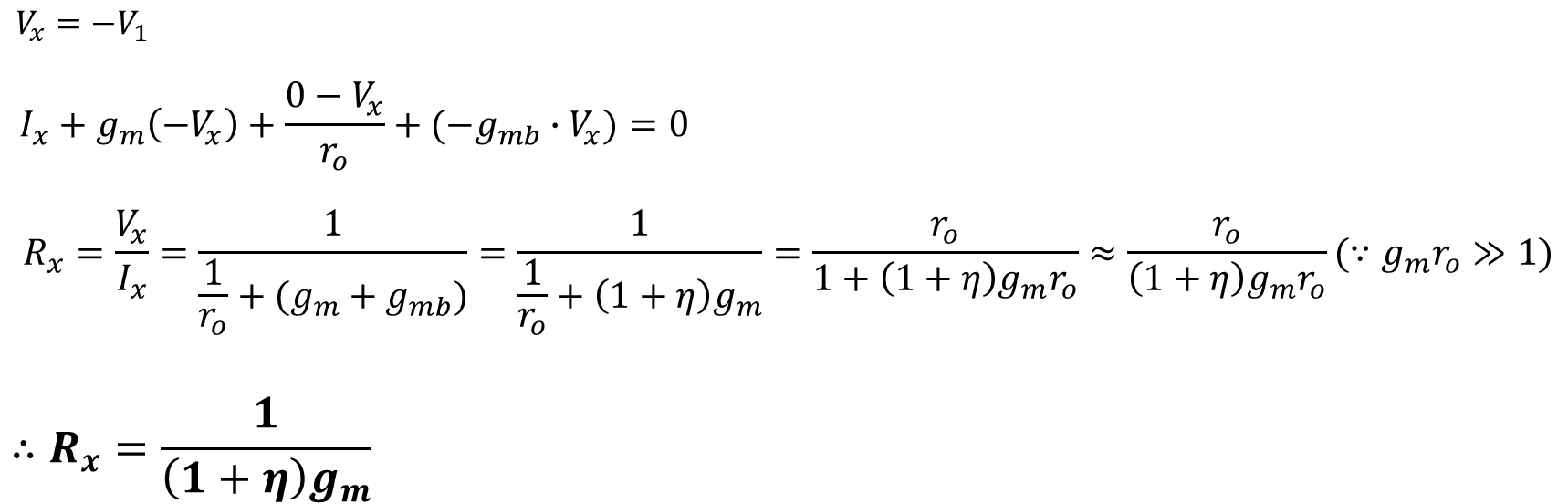

위의 상황들을 Vin이 커질 때 Vout에 대한 그래프로 표현하면 다음과 같이 나타낼 수 있다.

Common-Source(CS) Stage : Diode-Connected Load Small-Signal

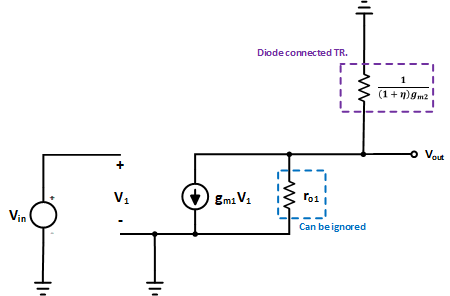

이번에는 Diode-Connected Load를 사용한 Common-Source amplifier의 소신호 분석을 해보자.

소신호 분석을 위해 Small-Signal Model로 표현하면 다음과 같이 나타낼 수 있다.

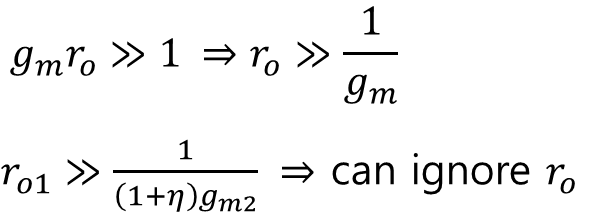

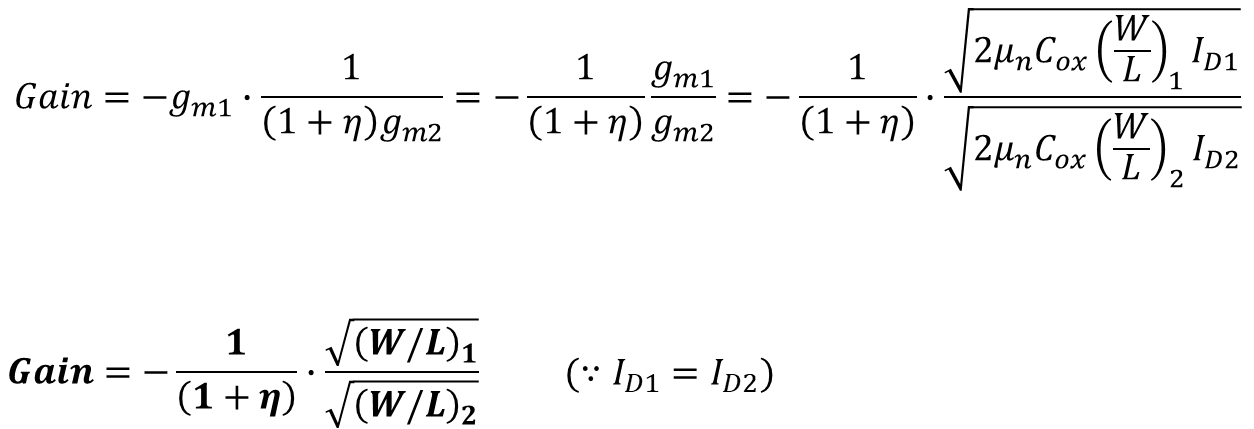

Small-Signal 분석은 Vout node에서 KCL을 적용하면 풀어낼 수 있다. KCL을 적용하여 Small-Signal Model을 해석하는 것은 앞과 동일하여 여기선 진행하지 않으려고 한다. 여기서는 어떻게 ro1이 생략되었는지 다루려고 한다. 간단하지만 한번 다루고 과정을 이해하는 편이 앞으로 자연스럽게 생략되는 과정에서 쉽게 이해될 것이다.

Small-Signal Model Analysis를 통해 Gain을 구해보면 다음과 같이 표현된다.

Diode-Connected Load를 사용한 CS Amp의 Gain은 신기하게 도출되었다. 바로 M1과 M2의 사이즈 비울로 결정됨을 확인할 수 있다. 이렇게 비율로 결정되는 설계를 ratiometric design이라고 부르며 PVT variation에 매우 강한 설계법이다.

하지만 Diode-Connected Load를 사용한 CS Amp의 Gain을 키우다 보면 문제점이 생기고 결국 새로운 방법을 찾게 된다. 이 내용들은 다음 장에서 다루도록 하겠다.

'회로설계 공부 > 기초 전자회로 이론' 카테고리의 다른 글

| [기초 전자회로 이론] Common-Source Stage의 Current Source Load에 대해 알아보자. (0) | 2022.04.03 |

|---|---|

| [기초 전자회로 이론] Common-Source Stage의 Large/Small - Signal Analysis에 대해 알아보자. (0) | 2022.03.31 |

| [기초 전자회로 이론] MOSFET의 Small-Signal Model에 대해 알아보자 (0) | 2022.03.30 |

| [기초 전자회로 이론] MOSFET의 Capacitance와 Multi Finger에 대해 알아보자. (1) | 2022.03.29 |

| [기초 전자회로 이론] MOSFET의 Secondary effects에 대해 알아보자. (0) | 2022.03.28 |