여기서 다룰 MOSFET의 구조와 동작 원리는 회로 해석에 도움이 될 간단한 수준의 얘기만 진행한다.

소자의 Doping 농도 결정, Fermi level과 같은 물리적 특성에 대해서는 논의하지 않는다.

MOSFET의 구조

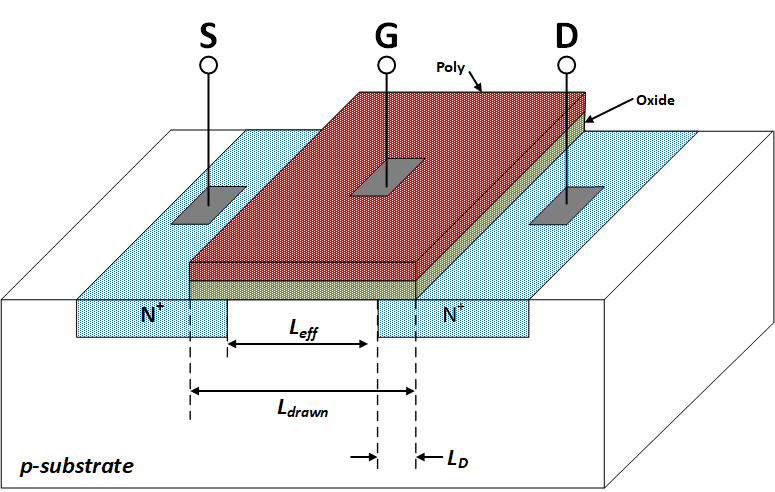

우리가 사용하는 MOSFET의 일반적인 구조(Planar mosfet structure)는 다음과 같다.

Oxide 위에 너비 W, 길이 L을 가지는 Polysilicon을 얹고 Polysilicon에 전압(VG)을 인가해 p-substrate의 전자를 모아 Source(S)와 Drain(D)를 연결해 Drain에서 Source로 전류가 흐를 수 있는 Channel을 만들어 줄 수 있는 구조이다. Mosfet 구조에서 실제 채널이 형성될 부분인 Effecitve length 인 Leff는 다음과 같이 표현할 수 있다. (LD는 Diffusion Length이다.)

위에서 보인 NMOS와 PMOS를 함께 사용한다. PMOS와 NMOS를 하나의 Wafer위에 올려서 사용할 수 있게 하기 위해 CMOS(Complementary Metal-Oxide-Semiconductor)라는 구조를 사용한다. CMOS의 구조는 아래와 같다.

MOSFET의 동작 원리

MOSFET이 Source와 Drain을 연결시켜 전류가 흐르게 하는 원리는 다음과 같다.

Gate 전압에 따라 소자의 변화를 알아볼 것이다.

① VGS < VTH

Gate 전압이 낮을 때 p-substrate에 있는 hole들이 Negative ion들을 남겨두고 밀려나게 된다.

이로 인해 Gate 아래에는 Depletion region이 형성된다.

전류를 흐르게 해 줄 수 있는 carrier는 존재하지 않아 전류가 흐르지는 않는 상태이다.

② VGS ≒ VTH

Gate의 전압이 높아지면서 Negative ion들이 전자를 남겨두고 밀려나게 된다.

이로 인해 Gate 아래에는 전자들이 쌓이게 된다. 이렇게 쌓인 전자들이 'Channel'을 형성한다.

이 채널은 Inversion layer라고도 부른다.

③ VGS ≒ VTH

Gate의 전압이 더욱 높아지면 Channel을 형성하는 전자들이 많아져 Drain에서 Source까지 수월하게 전류가 흐를 수 있도록 Channel이 커지게 된다.

위의 방식으로 MOSFET은 동작하게 된다.

Channel이 형성되어 전류가 흐를 수 있게 되는 최소의 Gate 전압을 Threshold Voltage(문턱 전압, VTH)라고 한다.

참고로 Threshold Voltage는 다음의 식으로 나타낼 수 있다. 회로 설계에는 사용될 부분은 아니라고 판단하여 해당 식이 도출되는 과정은 설명하지 않았다. 도출되는 과정이 궁금하다면 소자 해석에서 찾는 것을 추천한다.

위의 식에서 알 수 있는 부분은 Threshold 전압은 회로에서 변경할 수 없다는 점이다. 물론, 뒤에서 다룰 Body effect에 의해 변형되기 하지만, 이는 의도치 않은 변형이고 지금 원하는 것은 다양한 Thresold를 가진 MOSFET 소자이다. 이를 위해 파운드리 업체에서 제공하는 PDK(Process Design Kit)에는 VTH에 대한 여러 가지 옵션을 제공한다. Low VTH를 가지는 소자, High VTH를 가지는 소자 등을 제공해준다.

'회로설계 공부 > 기초 전자회로 이론' 카테고리의 다른 글

| [기초 전자회로 이론] MOSFET의 Secondary effects에 대해 알아보자. (0) | 2022.03.28 |

|---|---|

| [기초 전자회로 이론] MOSFET의 Transconductance에 대해 알아보자. (0) | 2022.03.27 |

| [기초 전자회로 이론] MOSFET의 전압과 전류의 관계에 대해 알아보자.(3) (0) | 2022.03.26 |

| [기초 전자회로 이론] MOSFET에서 전압과 전류의 관계에 대해 알아보자.(2) (0) | 2022.03.25 |

| [기초 전자회로 이론] MOSFET에서 전압과 전류의 관계에 대해 알아보자.(1) (0) | 2022.03.24 |